# **Topics**

- Minimising Boolean expressions

- Using Karnaugh maps

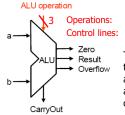

- ALU (Arithmetic Logic Unit)

- ALU design and implementation

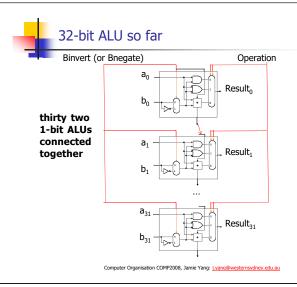

- 1-bit ALU

- 32-bit ALU

SONGS ABOUT COMPUTER SCIENCE .COMPUTER SCIENCE MAJOR? Written by Emmanuel Schanzer To the tune of: Hotel California http://www.cs.utexas.edu/users/walter/cssongbook/digital\_logic.html My mind is completely twisted My brain's completely snapped By these logic gates and Turin And those **Karnaudh maps** My mind is completely twisted My brain's completely snapped By these logic gates and Turing machines And those Karnaugh maps Registers dance in memory Clobbering the temps Some values you remember Some values you remember Some values you forget So I called up the professor Can I have more time? I haven't given an extension here since 1969

Computer Organisation COMP2008, Jamie Yang: i.yanq@westernsydney

#### Karnaugh maps: [I] State Sets State Sets for 2, 3 and 4-variable functions [a' stands for NOT a] ab ab' а ac\bd b′ b′ b b a′ a'b a'b' abc'd' abc'd ab'c'd ab'c'd а $2^2 = 4$ cases abcd' abcd ab'cd ab'cd' а a\bc b' b' b b a'bcd' a'bcd a'b'cd a'b'cd ahc' ahc ab'c ab'c' а a'bc'd a'b'c'd a'b'c'd' a'bc'd' a'bc' a'bc a'b'c a'b'c' a′ $2^4 = 16 \text{ cases } ----d----$ = 8 cases

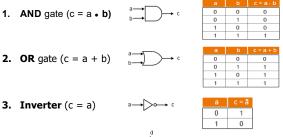

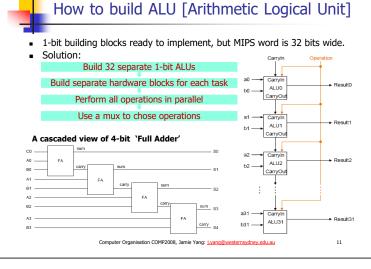

# Building blocks revisited

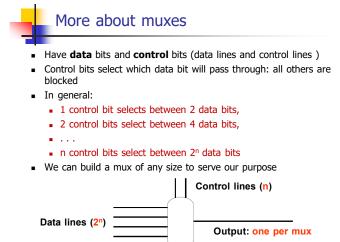

We will build ALU using four hardware building blocks:

4. Multiplexor (Mux) (if d = 0, c = a; else c = b)

## Karnaugh maps: [II] Truth Table

- Truth Tables

- determined by the internal functions

Computer Organisation COMP2008, Jamie Yang: <a href="mailto:juyang@westernsydney.edu.au">juyang@westernsydney.edu.au</a>

# Minimising Boolean expressions

- Before we start building ALU, consider how to minimise logic expressions in easy way, and implement circuits with as few logic

- For example, soon we will see that Carry Out formula expressed as a sum of products is (to be explained later):

CarryOut = (A'\*B\*CarryIn) + (A\*B'\*CarryIn) + (A\*B\*CarryIn') +(A\*B\*CarryIn)

...happens to be equivalent of:

CarryOut = (B\*CarryIn) + (A\*CarryIn) + (A\*B)

- But: the above simplification is not immediately obvious.

- Logic minimising tool which we will use is known as:

Karnaugh maps.

Computer Organisation COMP2008, Jamie Yang: j.yang@westernsydney.edu.au

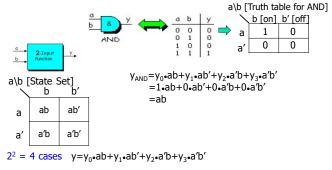

# Karnaugh maps: Simple mapping examples

2-input functions

Computer Organisation COMP2008, Jamie Yang: j.yr

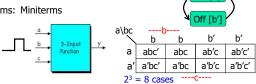

# Karnaugh maps

Product items: Miniterms

- Sum of Products  $y=y_0 \cdot abc' + y_1 \cdot abc + y_2 \cdot ab'c + y_3 \cdot ab'c' + ...$

- Use **Truth Table** to determine  $y_0, y_1, ...$

- Use Karnaugh maps (or K-maps) to simplify the expression

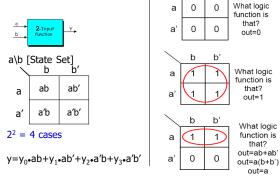

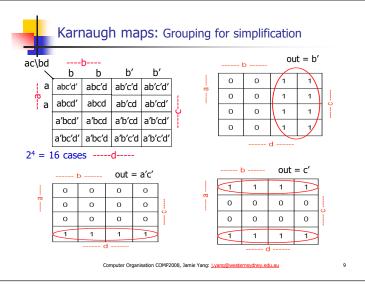

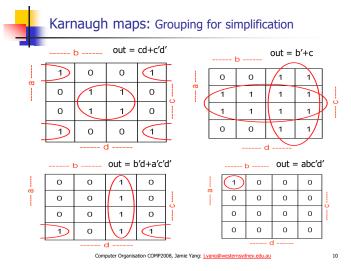

#### Karnaugh maps: Grouping for simplification

- Rules of grouping:

- of 1s

- side by side

- Rules of simplification "A change of one variable

- when crossing a horizontal or vertical boundaries of cells"

- Walk through a group

that?

out=1

out=a

- Invariables survive; changed ones eliminated

- Sum of net results of all groups (clusters)

#

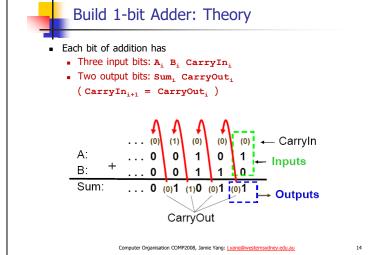

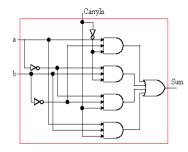

Build 1-bit Adder: implementation

- STEPS to implement the adder:

- 1. Construct the circuit for Sum

- 2. Construct the circuit for CarryOut  $\,$

- 3. Connect (1) and (2) together

Computer Organisation COMP2008, Jamie Yang: <u>i.yanq@westernsydney.edu.au</u>

(A'\*B\*CarryIn) + (A\*B'\*CarryIn) + (A\*B\*CarryIn') + (A\*B\*CarryIn')

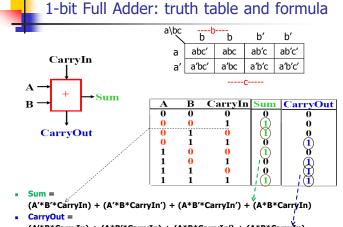

## 1-bit Full Adder: the Sum formula

- Can we simplify/minimise logic formulas for CarryOut and Sum for building the circuit using logic gates?

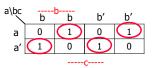

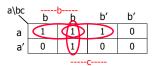

- Karnaugh table of the Sum formula: ... grouping 1s

simplification possible

Sum = (A'\*B'\*CarryIn) + (A'\*B\*CarryIn') + (A\*B'\*CarryIn') + (A\*B\*CarryIn)

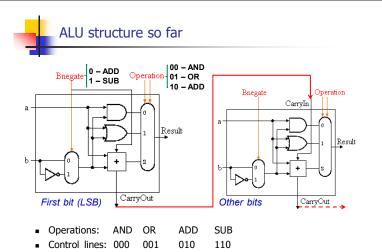

# ALU: Adder and Logical operations Logical Functions: AND, OR Arithmetic Operations Subtraction AND and OR CarryIn A 1-bit ALU that performs AND, OR and Addition. Mux "Operation" signal selects which operation is performed. CarryOut adde ation COMP2008, Jamie Yang: <u>i.ya</u>

# 1-bit Full Adder: the CarryOut formula

Karnaugh table of the CarryOut formula: ... grouping 1s

(B\*CarryIn) + (A\*CarryIn) +

### CarryOut

=(A'\*B\*CarryIn) + (A\*B'\*CarryIn) + (A\*B\*CarryIn') + (A\*B\*CarryIn) =(B\*CarryIn) + (A\*CarryIn) + (A\*B)

| \  | b     | b    | b′    | b′     |

|----|-------|------|-------|--------|

| а  | abc'  | abc  | ab'c  | ab'c'  |

| a′ | a'bc' | a′bc | a′b′c | a′b′c′ |

Computer Organisation COMP2008, Jamie Yang: <a href="mailto:j.yang@westernsydney.edu.au">j.yang@westernsydney.edu.au</a>

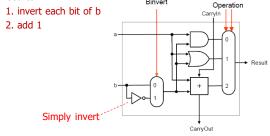

# Subtraction 1/3

- Subtraction: adding the negative version of an operand.

- Recall two's complement numbers: to create a negative number we need to:

How about 'add 1'?

Computer Organisation COMP2008, Jamie Yang: <a href="mailto:i.yang@westernsydney.edu.at">i.yang@westernsydney.edu.at</a>

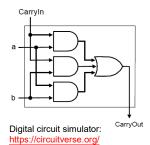

#### 1-bit Full Adder: formula -> circuit construction

■ For Sum

Sum=(A'\*B'\*CarryIn) + (A'\*B\*CarryIn')+ (A\*B'\*CarryIn') + (A\*B\*CarryIn)

■ For CarryOut

CarryOut=(B\*CarryIn) + (A\*CarryIn) + (A\*B)

Computer Organisation COMP2008, Jamie Yang: j.yang

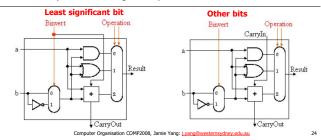

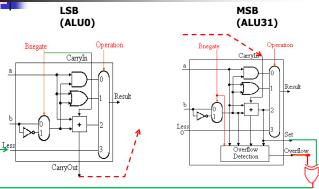

#### Subtraction 2/3

Notice that, the least significant bit still has CarryIn signal, which is never used for addition

- How CarryIn for ALU0 differs from other CarryIns?

- Initial CarryIn vs. Intermediate CarryIns.

- Initial CarryIn can be set at will

- If we set the Initial CarryIn bit to 1 instead of 0, we get: a+b+1

Computer Organisation COMP2008, Jamie Yang: j.yan

22

### 1-bit Full Adder: integrated circuit construction

Connect Sum and CarryOut together CarryOut STEP 1 (Sum) STEP 2 (CarryOut) CarryOut

ter Organisation COMP2008. Jamie Yann

#### Subtraction 3/3

- What happens if we now use Binvert for invert b and set the Initial CarryIn (at the least significant bit) to 1?

- The adder calculates: a+b+1 = a+(b+1) = a+(-b)=a-b

- This simplicity of hardware implementation of a two's complement adder is good illustration why two's complement representation is commonly used for integer computer arithmetics!

Computer Organisation COMP2008, Jamie Yang: <a href="mailto:j.yang@westernsydney.edu.au">j.yang@westernsydney.edu.au</a>

# Branch support

- Conditional branch instructions switch either if two registers are equal, or if they are not equal:

- beq register1, register2, label (example: beq \$\$4,\$\$2, LABEL1)

- bne register1, register2, label (example: bne \$s1,\$s3, L7)

- How to test that contents of two register is equal?

- a = b means (a b) = 0

- How to implement the above:

- Subtract b from a

- Add hardware to test if the result is zero

- OR all the outputs together, and invert the output:

Zero =

$$\overline{\text{(Result1 + Result2 + .. + Result31)}}$$

variable

$$= \begin{cases} 1 \text{ (true)} & \text{if } (a - b) = 0 \text{ holds} \\ 0 \text{ (false)} & \text{else} \end{cases}$$

Next slide show additional hardware for branch support :

Computer Organisation COMP2008, Jamie Yang: <a href="mailto:j.yang@westernsydney.edu.au">j.yang@westernsydney.edu.au</a>

25

32-bit ALU with branch support

Operation

Operation

Operation

Operation

Operation

Zero detector:

1 (a = b holds)

O otherwise

Computer Organisation COMP2008, Jamie Yang: j.yanq@westernsydney.edu.a

4

# Set on less than (slt) support

slt rd, rs, rt

$$rd := -\begin{bmatrix} 1 & \text{if (rs < rt)} \\ 0 & \text{else} \end{bmatrix}$$

■ Implement the idea in ALU

MSB

[determines the sign]

- modify 1-bit ALU for the most significant bit (ALU31 for bit 31):

- a new output line (**Set** 1 bit) used only for slt

- (by the way we added overflow detection logic, also associated with this bit)

- new input line (Less 32 bits) goes directly to mux

- New control line (111) for slt

Computer Organisation COMP2008, Jamie Yang: j.yanq@westernsydney.edu.au

+

#### Shift instructions

- What is left:

- logical and arithmetic shifts sll, srl, sra

- Need a new data line for a shifter (L and R)?

- however shifters are much more easily implemented outside the ALU.

- 1-bit ALU: integrated block notation

AND OR ADD SUB .

000 001 010 110

The symbol commonly used

to represent ALU. It is also used to represent an adder, so it is labelled ALU or Adder.

CarryOut

31

# 4

#### ALU with slt support

# 4

# Revision and quiz

Given the following Karnaugh map. The output can be expressed by out = c'.

In 1-bit full Adder, the circuit construction for 'CarryOut' is correct:

How ALU is used to support the branch instruction? beq register1, register2, label

PH6: Appendix B: The Basics of Logic Design PH5: Appendix B: The Basics of Logic Design PH4: Appendix C: The Basics of Logic Design Text readings are listed in Teaching Schedule and Learning Guide

PH6 (PH5 & PH4 also suitable): check whether eBook available on library site

PH6: companion materials (e.g. online sections for further readings)

https://www.elsevier.com/books-andjournals/bookcompanion/9780128201091

PH5: companion materials (e.g. online sections for further readings) http://booksite.elsevier.com/978012407 7263/?ISBN=9780124077263

Computer Organisation COMP2008, Jamie Yang: <a href="mailto:1.yang@westernsydney.edu.a">1.yang@westernsydney.edu.a</a>

33