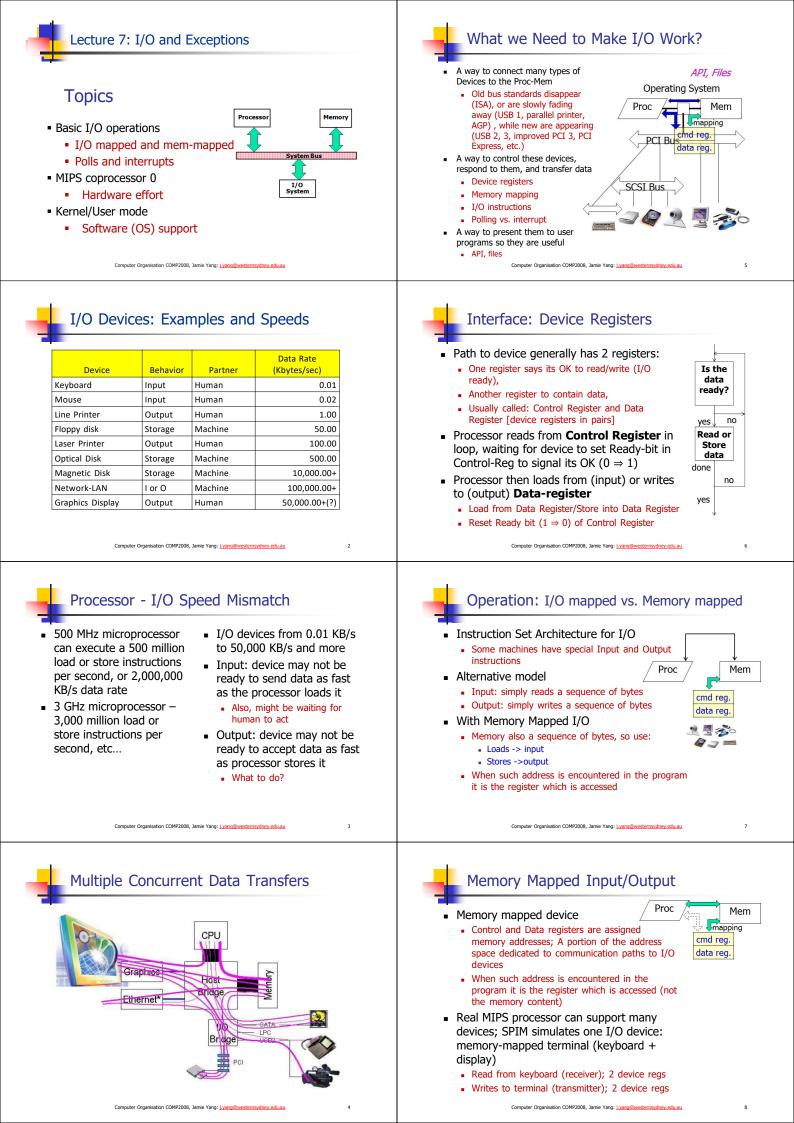

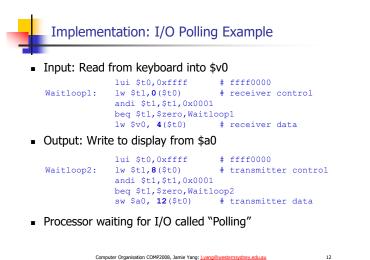

### Memory Mapped I/O: SPIM I/O Simulation

- Certain addresses are not regular memory

- Instead: they correspond to registers in I/O devices

# Memory Mapped I/O: SPIM I/O Simulation

- Control register rightmost bit (bit-0): Ready

- It cannot be changed by processor (just like \$0)

- Receiver: Ready==1 means character in Data Register arrived but not yet been read;

- $1 \Rightarrow 0$  when data is read from Data Register

- **Transmitter**: Ready==1 means transmitter is ready to accept a new character;

- $\mathbf{0} \Rightarrow \mathsf{Transmitter}$  still busy writing last char

- Data register rightmost byte has data

- **Receiver**: last char from keyboard; rest = 0

- **Transmitter**: when rightmost byte written, writes character to display

Computer Organisation COMP2008, Jamie Yang: j.yang@westernsydney.edu.au

10

11

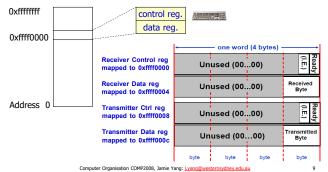

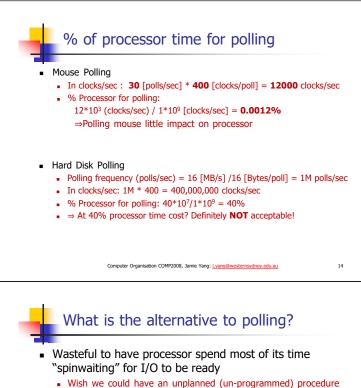

Polling overhead can consume a lot of CPU time

Computer Organisation COMP2008, Jamie Yang: j.yang@westernsydney.ed

#### Performance: Cost of Polling?

Assume for a processor with a 1 GHz clock, it takes

400 clock cycles for a polling operation (call polling routine, accessing the device, and returning). Determine

% of processor time for polling.

| Mouse       | Polled <b>30 times/second</b> (polling frequency) so as not to miss user movement                                                                |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Floppy disk | Transfers data in 2-byte units ( <b>2-bytes/poll</b> ) and has a data rate of <b>50 KB/second</b> . No data transfer can be missed.              |

| Hard disk   | Transfers data in 16-byte chunks ( <b>16-bytes/poll</b> ) and can transfer at <b>16 MB/second</b> (data rate). Again, no transfer can be missed. |

Computer Organisation COMP2008, Jamie Yang: j.yang@westernsydney.edu.au

13

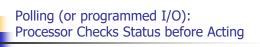

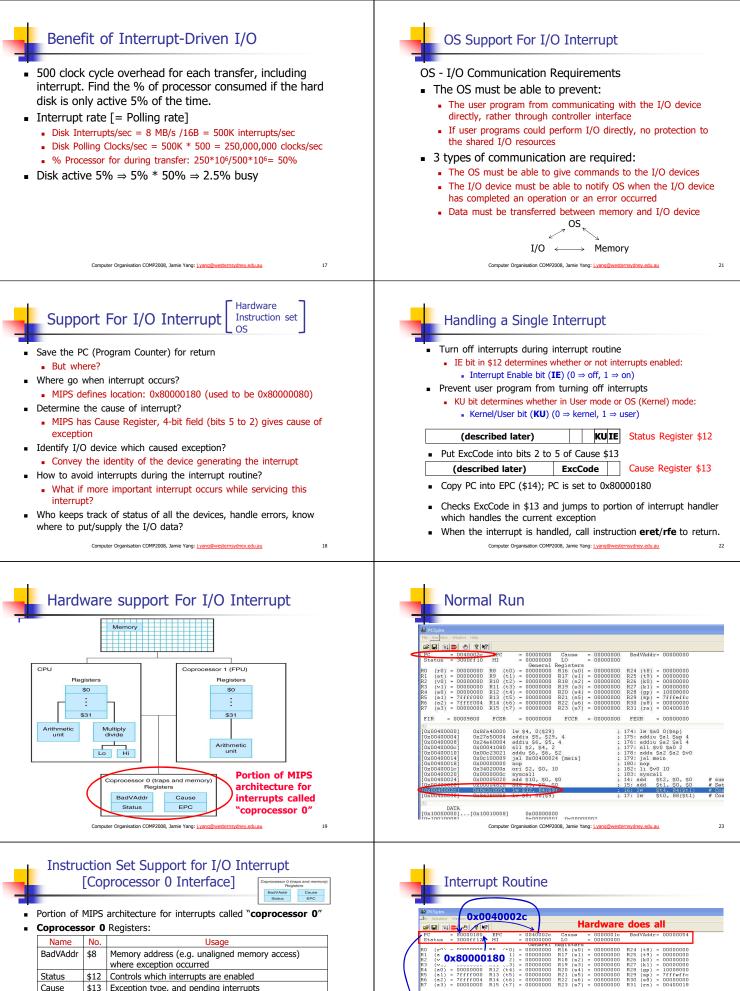

- call that would be invoked only when I/O device is ready...

- Use exception mechanism (as in arithmetic overflow)!

- interrupt program when I/O ready,

- return when done with data transfer

- An I/O interrupt is just like the exceptions except:

- More information needs to be transferred

- An I/O interrupt is asynchronous with respect to instruction execution

- It does not prevent any instruction from completion

Pick convenient point to take an interrupt, let the current instruction complete

16

15

BadVAddr \$8 Memory address (e.g. unaligned memory access) where exception occurred Status \$12 Controls which interrupts are enabled Cause \$13 Exception type, and pending interrupts EPC \$14 PC (address of instruction) that caused exception Coprocessor 0 Instructions Data transfer: lwc0, swc0 [c0::reg ---- mem] Move: (from) mfc0, (to) mtc0 [reg ---- c0::reg] A few examples: Iwc0 \$8, 0(\$a0) mfc0 \$k0, \$14 # \$k0 ← c0::\$14, move contents of EPC to register \$k0 • mtc0 \$0, \$13 # \$0  $\rightarrow$  c0::\$13, clears cause register (c0::\$13 gets 0).

im \$2, 520;2;

: 84: sw \$v0 s1

sw \$2, 521;(\$1]

interrupt

lui \$1, -28672;

interrupt

sw \$4, 516(\$1]

: 85: sw \$a0 s2

mfc0 \$26, 513;

. Forutine

sr1 \$4, 526, 2

: 87: smfc0 \$k0

sr1 \$4, sr1 \$a0 \$k0

: 88: sr1 \$a0 \$k1

0x00000000 0x0000001 0x0000002 0x0000003 0x0000004 0x0000005 0x0000006

FCCR

- 00000000

FEXR

; 36: syscall ; 37: jr Sra ; 38: add \$0, \$0, \$0

: 87: mfc0 \$k0 \$13 : 88: sr1 \$a0 \$k0 \$

- 00000000

R12 (t R13 (t R14 (t) R15 (t

FCSR

0xac220200 0x3c019000 0xac240204 0x401a6800 0x001a2082

.[0x10010008]

0x8c240000 lw \$4, 0(\$1) [s 0x000000c syscall 0x03e00008 jr \$31 0x00000020 add \$0, \$0, \$0

- 00000000

1w \$4, 0(\$1) [sum]

(V.) (a0) = 00000000 (a1) = 7fff000 (a2) = 7fff004 (a3) = 0000000

FIR

- 00009800

74

# ret # nop

/ Sav / Not

# Bu1

# Cau # Ext

#### Example Interrupt Routine

Place at 0x80000180

.ktext 0x80000180

mfc0 \$k0,\$13

# \$13 is Cause reg # \$14 is EPC reg

25

26

27

28

• Exception field is bits 5 to 2;  $0000 \Rightarrow I/O$

Read byte

mfc0 \$k1,\$14

sw \$ra, save0(\$0) # save old \$31

jal ReadandStoreByte

lw \$ra, save0(\$0) # restore \$31

jr \$k1

Computer Organisation COMP2008, Jamie Yang: <u>i.yang@westernsydney.e</u>

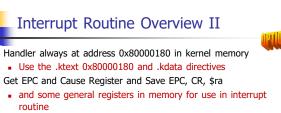

## Interrupt Routine Overview I

- Handler always at address 0x80000180 in kernel memory

Use the .ktext 0x80000180 and .kdata directives

- Must save and later restore all registers used

- \$v0, \$a0, \$ra, Cause and EPC register

- Including \$at use .set noat to suppress SPIM's errors

- Can temporarily spill registers to .kdata, or move to \$k0 and \$k1 (used freely); Should not use stack – may point to invalid memory

- Parse exception code field from Cause register, and jal via jump table to appropriate routine based on ExpCode field in Cause (I/O interrupt, System call, Arithmetic Overflow)

- Mmaintaining a jump table

- Restore saved registers; return control to the user program with eret (for MIPS32) or rfe (for MIPS-I (R2000))

- Jumps to EPC, and resets Exception level in Status

- Computer Organisation COMP2008, Jamie Yang: <u>i,vang@westemsydney.edu.au</u>

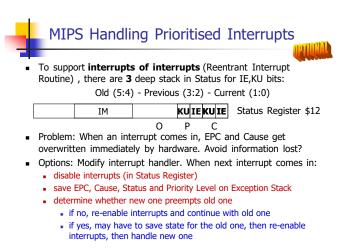

## Multiple Interrupts

- Problem: what if we're handling an Overflow interrupt and an I/O interrupt comes in?

- Options:

- drop any conflicting interrupts: unrealistic, they may be important

- simultaneously handle multiple interrupts: unrealistic, may not be able to synchronize them

- queue them for later handling: sounds good

- Problem: how to handle them in order of urgency?

- Options:

- We need to categorize and prioritize interrupts some interrupts have higher level of priority

Computer Organisation COMP2008, Jamie Yang: j.yang@westernsydney.edu.au

#### Prioritizing Interrupts - Interrupt Priority Levels in MIPS

- MIPS architecture enables 5 levels of HW priorities and 3 levels of SW priorities, from highest level to lowest level (8 IPLs):

- Bus error

- ...Illegal Instruction/Address trap

- High priority I/O Interrupt (fast response)

- Low priority I/O Interrupt (last response)

- (these are the levels of interest now)

- Interrupt Levels in MIPS also differ by applications

- It depends what the MIPS chip is inside of:

- PalmPC, Sony Playstation 3, PSP, HP LaserJet printer, etc.

|   | MIPS Handling Prioritised Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| - | Processor always executing at one IPL Interrupt handlers and device drivers pick IPL to run at, this gives faster response for some interrupts Crisp cases If processor runs at <b>lowest</b> IPL level: any interrupt accepted                                                                                                                                                                                                                                                                                                                                                                            |

|   | If processor runs at highest IPL level: all interrupts ignored                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | <ul> <li>Soft cases</li> <li>If processor runs at some IPL level: an interrupt accepted only if IE==1 and<br/>Interrupt Mask (IM) bit == 1 for its level (that no higher priority interrupts.)</li> <li>If an interrupt occurs when Mask bit is off: don't ignore, but pending. Cause<br/>register has a field - Pending Interrupts (PI) bits (bits 15:11) for each of the 5<br/>HW interrupt levels - corresponding bit becomes 1 when an interrupt at its level<br/>has occurred but was not yet serviced.</li> <li>Interrupt routine checks IM ANDed with PI to decide what to service next.</li> </ul> |

|   | <sup>15</sup> IM <sup>8</sup> KUIE Status Register \$12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   | 15         PI         11         ExcCode         Cause Register \$13           Computer Organisation COMP2008, Jamie Yang: <u>Jyang&amp;westernsydney.edu.au</u> 29                                                                                                                                                                                                                                                                                                                                                                                                                                        |

Computer Organisation COMP2008, Jamie Yang: j.yang@westernsydney.edu.au

- If I/O, Cause Register PI field ANDed to Status Register IM field to find unmasked interrupts (maybe several); pick the highest

- Change IM of Status Register to inhibit current level and lower priority interrupts

- Change Current IE of Status Register to enable interrupts

only higher priority interrupts will get through

- Jump to appropriate interrupt routine (using jump table)

- On Return, restore saved registers, return control to the user program with eret / rfe

- Jumps to EPC, and resets Exception level in Status

Computer Organisation COMP2008, Jamie Yang: <u>iyang@westernsydney.edu.au</u>

- Device registers are a good abstraction to represent devices in memory-mapped I/O organisation:

True

False

- Why I/O Polling is less efficient than I/O Interrupt?

- What do the following instructions preform respectively? mfc0 \$k0, \$14 # mtc0 \$0, \$13 #

- For more see lab 10: exception handler code, and additional notes.

32

30

31

Text readings are listed in Teaching Schedule and Learning Guide

PH6 (PH5 & PH4 also suitable): check whether eBook available on library site PH6: companion materials (e.g. online sections for further readings) https://www.elsevier.com/books-and-

journals/bookcompanion/9780128201091 PH5: companion materials (e.g. o

PH5: companion materials (e.g. online sections for further readings) http://booksite.elsevier.com/978012407 7263/?ISBN=9780124077263

33

Computer Organisation COMP2008, Jamie Yang: j.yang@westernsydney.edu.au