### **Topics**

### SONGS ABOUT COMPUTER SCIENCE

The MIPS Instruction Set

Written by Walter Chang

To the tune of: The Major-General's Song

http://www.cs.utexas.edu/users/walter/cs-sondbook/instruction set.html

There's sh and sb and lbu and blez and jal and then sltu

And of course there's and and add and sri and sub and things to do

With the MIPS instructions I am very nimble on my feet

And though I sing assembler but I am really not a geek

There's addu, ori, slti, swr, and bgez and jair too And loads of other fun instructions that were put in just for you The MIPS instruction set is very simple to be memorized Which will come in handy when you have your code to be optimized

MIPS Assembly Language

■ RISC: Principles of good design

R, I, J instruction formats

• Data access: Use registers; memory addressing

■ Data process: Arithmetic instructions

• Programming constructs: Controlling flow of instructions

branches, if statement, loops, switch statement

Computer Organisation COMP2008, Jamie Yang: j.yanq@westernsydney.edu.au

## 1

### MIPS arithmetic

Simple statements

A complex statement

C code: f = (g + h) - (i + j);

MIPS code: add t0,g,h # temp regs?

add t1,i,j #

sub f,t0,t1 #

Computer Organisation COMP2008, Jamie Yang: <a href="mailto:j.yanq@westernsydney.edu.a">j.yanq@westernsydney.edu.a</a>

### Language of the machine, RISC, CISC

- Language of the machine

- Instructions

- More primitive than statements in higher level languages

- Very restrictive formats

- Design goals are:

- RISC: Reduced Instruction Set Computer

- all instructions are simple, the same length

- also known as load / store architecture

- Another architecture: CISC (Complex ...)

- current example: Intel

- Is there a clear line distinguishing RISC and CISC?

Computer Organisation COMP2008, Jamie Yang: <a href="mailto:j.yang@westernsydney.edu.ar">j.yang@westernsydney.edu.ar</a>

## 1

### Registers as operands

- In MIPS arithmetic instructions operands must be registers

- MIPS: 32 registers, each 32-bit wide, 32 bits is a word

- A complex statement again PROPERLY coded:

C code: f = (g + h) - (i + j);

MIPS code: add \$t0,\$s1,\$s2 # add \$t1,\$s3,\$s4 # sub \$s0,\$t0,\$t1 #

- Compiler associates variables with registers

- lots of variables more registers?

2nd principle of good design: Smaller is faster

Computer Organisation COMP2008, Jamie Yang: <a href="mailto:j.yanq@westernsydney.edu.au">j.yanq@westernsydney.edu.au</a>

### Typical Operations (little change since 1960)

| Data Movement         | Load (from memory), Store (to memory) memory-to-memory move, register-to-register move input (from I/O device), output (to I/O device) push, pop (to/from stack) |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Arithmetic            | Add, Subtract, Multiply, Divide integer (binary + decimal) or FP                                                                                                 |

| Shift                 | shift left/right (logical / arithmetic), rotate left/right                                                                                                       |

| Logical               | not, and, or, xor, set, clear                                                                                                                                    |

| Control<br>(J/Branch) | unconditional, conditional                                                                                                                                       |

| Subroutine<br>Linkage | call, return                                                                                                                                                     |

| Interrupt             | trap, return                                                                                                                                                     |

| Synchronisation       | test & set (atomic read-mod-write)                                                                                                                               |

| String                | search, translate                                                                                                                                                |

| Graphics              | parallel subword ops (4 16bit add)                                                                                                                               |

Computer Organisation COMP2008, Jamie Yang: <u>i.yanq@westernsydney.edu.au</u>

### Use immediate values – part 1/2

```

program to calculate ? = (5 - 20) - (13 + 3)

-20, 13, 3 are in registers $s1 through $s4

# assumes: Numbers 5,

.data

.globl mess

.asciiz "\nThe value of f is: " # string to print

.text

.globl main

# main has to be a global label

addu $s7,$0,$ra

# save the return address in $s7

# the actual calculations follow: # initialisation and move

# immediate numbers to registers

addi $s1.$0.5

# $s1 <= 5

<=> s1=5: (C-like)

# $s2 <= -20 <=> s2=-20;

addi $s2,$0,-20

addi $s3,$0,13

# $s3 <= 13

<=> s3=13;

addi $s4,$0,3

# $s4 <= 3

<=> s4=3;

add $t0,$s1,$s2

# 5 - 20

<=> t0=s1+s2;

# 13 + 3

<=> t1=s3+s4;

add $t1,$s3,$s4

sub $s0,$t0,$t1

# ? = (5 - 20) - (13 + 3)

\# <> s0 = (s1 + s2) - (s3 + s4);  Computer Organisation COMP2008, Jamie Yang: \underline{i,yang@westernsydney.edu.au}

```

### MIPS arithmetic

HP4 Section 2.2 P77-P80

All instructions have 3 operands with fixed order: destination first. Simpler hardware!

Examples:

C assignment statement: a = b + cCorresponding MIPS code: add a,b,c

C assignment statement: a = b + c + d + eMIPS code:  $add\ a,b,c\ \#$   $add\ a,a,d\ \#$  $add\ a,a,e\ \#$

1st principle of good design (more later, there are 4): Simplicity favours regularity

### Use immediate values – part 2/2

| li \$v0,4              | # 1 | HP.                | _AppA.pdf  | Page 4       | 4 or Ap          | pendix B                     | in HP4            |

|------------------------|-----|--------------------|------------|--------------|------------------|------------------------------|-------------------|

| la \$a0,mess           | #   |                    |            | Service      | System call code | Arguments                    | Result            |

|                        |     |                    |            | print int    | 1                | \$30 = integer               |                   |

| syscall                | #   |                    |            | print_float  | 2                | Sf12 = float                 |                   |

| 0,00022                |     | •                  |            | print_double | 3                | \$f12 = double               |                   |

| 1: 00 1                | #   |                    |            | print_string | 4                | \$20 = string                |                   |

| 11 900,1               | #   | •                  |            | read_int     | 5                |                              | integer (in \$VO) |

| 11 4 0 40 4 0          |     |                    |            | read_float   | 6                |                              | float (in \$ f()) |

| add \$a0,\$0,\$s0      | #   |                    |            | read_double  | 7                |                              | double (in \$ f0) |

|                        |     |                    |            | read_string  | 8                | \$30 = buffer, \$31 = length |                   |

|                        |     | address (in \$ v0) |            |              |                  |                              |                   |

| -1                     |     |                    |            | ex1t         | 10               |                              |                   |

|                        |     |                    |            |              |                  |                              |                   |

| WOSUAL SCULL AC CHE EN | u   | ,_                 | the main   |              |                  |                              |                   |

| - 44 6 60 6-5          | - ш |                    |            |              |                  |                              |                   |

| addu şra,şu,şs,        | / # | r                  | estore the | retur        | n addre          | ISS                          |                   |

|                        |     |                    |            |              |                  |                              |                   |

| jr \$ra                | #   | r                  | eturn to t | the mai      | n progr          | am                           |                   |

```

# program to calculate f = (g + h) - (i + j)

assumes: variables f through j are in registers $s0 through $s4

.data

.glob1 mess

asciiz "\nThe value of f is: " # string to print

# f = 0

# simple/single variables

f:

word 0

g:

.word 5

word -20

# similar usage also as in lab 4 code

.word 13

# simplemem.s

j:

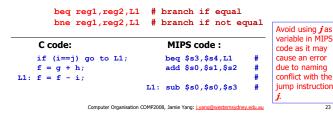

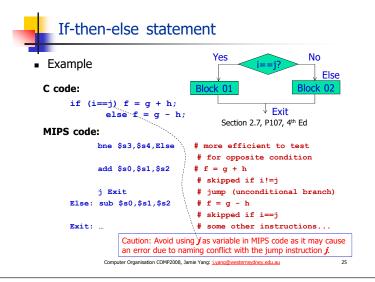

Caution: Avoid using j as variable in MIPS code as it may cause

an error due to naming conflict with the jump instruction \boldsymbol{j}.

# main has to be a global label

addu $s7,$0,$ra

# save the return address in $s7

actual calculations follow:

# $s1 <= g = 5;

# $s2 <= h = -20;

lw $s1,g

lw $s2,h

lw $s4, j

# $s4 <= j = 3;

```

Use simple variables (see lab code) – part 1/2

#### lw and sw Array element HP4 Section 2.2 P83-P85 Example (result in register, lw): g = h + A[8];C code: MIPS code: lw \$t0,32(\$s3) #how to declare an array? add \$s1,\$s2,\$t0 # Address (leading cell) Offset (byte) Indices (word) $k*4+A \rightarrow k*4(A)$ k\*4A[8] 32+A A[1] 4+A → 4(A) 1 \* 4=4 k = 1A[0] 0 \* 4 = 0 $0+A \rightarrow 0(A)$ ion COMP2008, Jamie Yang:

### Use simple variables (see lab code) – part 1/2

```

add $t0,$s1,$s2  # g + h

add $t1,$s3,$s4  # ???

sub $s0,$t0,$t1  # ???

li $v0,4  # HP_AppA.pdf Page 44 or Appendix B in HP4

la $a0,mess  # . . .

syscall  # . . .

add $a0,$0,$s0 # . . .

syscall

#Usual stuff at the end of the main

addu $ra,$0,$s7  # restore the return address

jr $ra  # return to the main program

```

$Computer\ Organisation\ COMP2008,\ Jamie\ Yang: \underline{i.vanq@westernsydney.edu.au}$

# 4

### lw and sw

Example (result in register, lw):

Computer Organisation COMP2008, Jamie Yang: <a href="mailto:i.yanq@westernsydney.edu.au">i.yanq@westernsydney.edu.au</a>

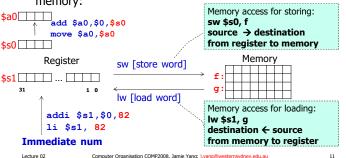

#### MIPS data transfer

- Registers are adequate for immediate numbers and simple variables

- MIPS instructions to move data between registers and memory:

10

### Using array index

Example:

C code: q = h + A[i];MIPS code: # \$t1 := i the word index; calculate offset 4\*i add \$t1.\$t1.\$t1 # \$t1 = i + i = 2i# \$t1 = 2i + 2i = 4iadd \$t1,\$t1,\$t1 # adding replaces mult # \$s3 := A the base address; calculate 4\*i + A add \$t1,\$t1,\$s3 # \$t1 = address of A[i] lw \$t0,0(\$t1) # \$t0 gets A[i] # \$s2 := h add \$s1,\$s2,\$t0 # g (reg \$s1) gets result lw \$t0, \$t1(\$s3) # ?? \$t1 + \$s3

Computer Organisation COMP2008, Jamie Yang: <a href="mailto:j.vanq@westernsydney.edu.au">j.vanq@westernsydney.edu.au</a>

### Complex data structures - Array in memory

Registers are adequate for numbers or simple variables

```

Arrays may have more elements than registers available

Example (A[...] in memory): 1. How to declare an array?

int A[13];

Name – Base address

C code:

a = b + A[8]:

Size – Number of elements

Type – Block size of single

2. How to locate and access

an array element? Index

A[8]

Offset from base

3. Physical address A[k]

Offset Base

k*4 + A

A[1]

4. How to define an array A?

5. How to load A to register?6. How to calculate k * 4 ? ...

7. Addressing syntax x(y)

Offset(Base); B(O); 0(B+O)

A[0]

```

uter Organisation COMP2008, Jamie Yang: j.yang@westernsydney.edu.au

### 4

### Spilling registers

- Registers are faster than memory

- smaller is faster

- registers are faster to access and easier to use

- In RISC, data can only be operated on in registers !!!

- If more variables than registers: spilling registers

- compiler must use registers efficiently for high performance

# \$t1 := i the word index; calculate offset 4\*i

# \$t1 := i the word index; calculate offset 4\*i

add \$t1,\$t1,\$t1 # \$t1 = i + i = 2i

add \$t1,\$t1,\$t1 # \$t1 = 2i + 2i = 4i

# \$s3 := A the base address; calculate 4\*i + A

add \$t1,\$t1,\$s3 # \$t1 = address of A[i]

3rd principle of good design:

Good design demands good compromises

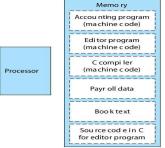

### Stored Program Concept

- Programs are stored in memory

- Instructions are represented as numbers (consisting of bits)

- to be read or written just like data

Translating machine language

18

• the first and the last field in combination specify "add"

• the second, third, and fourth field specify two source registers,

and the destination register -- registers are represented as

Computer Organisation COMP2008, Jamie Yang: j.yang@westernsydney.edu.au

Each instruction consists of fields

17

number between 0 and 31

For example: add \$t0,\$s1,\$s2

Instructions, like registers and words are 32-bit long

• each field is represented as a number, and has a specific meaning

Section 2.5, P101, 4th Ed

See HP4, P134 and instruction decoding.pdf on vUWS

0

32

### Exercise example

**EXERCISES**

Can you figure out the code? (C followed by MIPS)

Computer Organisation COMP2008, Jamie Yang: j.yang@

There will be many exercises.

(or: additional, NON GRADED homework)

The exercises WILL help you to better:

understand the material covered, prepare you for labs, prepare you for final exam.

Here is the first one:

swap(int v[], int k) C code: { int temp; temp = v[k]; v[k] = v[k+1]; v[k+1] = temp;

MIPS code:

add \$t0,\$a1,\$a1 add \$t0,\$t0,\$t0 # \$t0 = 4k add \$t0,\$a0,\$t0 # \$t0 = address of v[k]lw \$t1,0(\$t0) # \$t1 = v[k]lw \$s0,4(\$t0) # \$s0 = v[k+1]sw \$s0,0(\$t0) # v[k] = \$s0sw \$t1,4(\$t0) # v[k+1] = \$t1jr \$ra # return

Computer Organisation COMP2008, Jamie Yang: j.yang

### MIPS Register Convention

the fifth field is unused in this instruction

Important – keep a copy of this page!

| Name        | Register<br>Number | Usage                            | Preserve on call? |

|-------------|--------------------|----------------------------------|-------------------|

| \$zero      | 0                  | constant 0 (hardware)            | n.a.              |

| \$at        | 1                  | reserved for assembler           | n.a.              |

| \$v0 - \$v1 | 2-3                | returned values                  | no                |

| \$a0 - \$a3 | 4-7                | arguments                        | yes               |

| \$t0 - \$t7 | 8-15               | temporaries                      | no                |

| \$s0 - \$s7 | 16-23              | saved values(declared variables) | yes               |

| \$t8 - \$t9 | 24-25              | temporaries                      | no                |

| \$k0, \$k1  | 26, 27             | reserved for OS kernel           | n.a.              |

| \$gp        | 28                 | global pointer                   | yes               |

| \$sp        | 29                 | stack pointer                    | yes               |

| \$fp        | 30                 | frame pointer                    | yes               |

| \$ra        | 31                 | return address (hardware)        | yes               |

### Controlling the flow of instructions

- Decision making instructions

- alter the control flow (the "next" instruction)

- distinguishes a computer from a simple calculator

- In a high level language if statement, go to statement

- In an assembly language *jumps*, conditional *branches*

- MIPS conditional branch instructions:

### Instruction Formats: R, I, J types

R-type Instruction format (R for Register)

| ор     | rs     | rt     | rd     | shamt  | funct  |

|--------|--------|--------|--------|--------|--------|

| 6 bits | 5 bits | 5 bits | 5 bits | 5 bits | 6 bits |

I-type Instruction format (I for Immediate)

| ор     | rs     | rt     | constant |

|--------|--------|--------|----------|

| 6 hits | 5 bits | 5 bits | 16 hits  |

■ J-type Instruction format (J for Jump)

| ор     | address |

|--------|---------|

| 6 bits | 26 bits |

ter Organisation COMP2008, Jamie Yang: j.yang@y

### Control Flow

We have *beq, bne*, what about Branch-if-less-than?

```

blt $s0,$s1,Less

# pseudoinstruction

```

New instruction "set on less than":

```

slt $t0,$s0,$s1

bne $t0,$zero,Less

```

### {condition checking, looping block, occurrence updating}

Simple loop:

```

C code (pseudo code): Loop: g = g + A[i];

i = i + j;

if ( i != h ) go to Loop

MIPS code:

Loop: add $t1.$s3.$s3

# $t1 = 2i

add $t1,$t1,$t1

# $t1 = 4i

add $t1,$t1,$s5

# $t1 = address of A[i]

# $s5=array base address

lw $t0,0($t1)

# $t0 = A[i]

add $s1,$s1,$t0

#g=g+A[i]

add $s3,$s3,$s4

#i=i+j

bne $s3,$s2,Loop

# if i != h

# next instruction...

```

Computer Organisation COMP2008, Jamie Yang: <a href="mailto:j.yang@westernsydney.edu.au">j.yang@westernsydney.edu.au</a>

### Revision

Given the register and memory values in the tables below (with dummy data for easy calculation), work out the contents of registers in the instructions.

| Register | Value | Memory Location | Value |

|----------|-------|-----------------|-------|

| R1       | 12    | 16              | 20    |

| R2       | 16    | 20              | 12    |

| R3       | 20    | 24              | 16    |

| R4       | 24    | 28              | 24    |

lw R3, 12(R1) addi R2, R3, 12

ISA and MIPS implementation

**MIPS**

while loops:

| Willie 100 | <b>DS.</b> |                              | as variable in MIPS |

|------------|------------|------------------------------|---------------------|

| C code:    | while      | (save[i] == k)<br>i = i + j; |                     |

|            |            |                              |                     |

de as it may cause error due to naming nflict with the jump instruction j. MIPS code:

Loop: add \$t1,\$s3,\$s3 # \$t1 = 2i add \$t1.\$t1.\$t1 # St1 = 4iadd \$t1,\$t1,\$s5 # \$t1 = address of save[i] # \$s5=array base address lw \$t0,0(\$t1) # \$t0 <= save[i] bne \$t0,\$s2, Exit # test condition, \$s2 has kadd \$s3,\$s3,\$s4 # i = i + jj Loop # keep looping Exit: # next instruction...

Caution: Avoid using j

Computer Organisation COMP2008, Jamie Yang: j.yang@westernsydney.edu.au

**ASCII TABLE**

#### See ascii\_chart.pdf on vUWS

| DEC | HEX | CI       | IAR       | DEC      | HEX       | CHAR      | DEC      | HEX       | CHAR     | DEC | HEX | CI  |

|-----|-----|----------|-----------|----------|-----------|-----------|----------|-----------|----------|-----|-----|-----|

|     |     |          |           |          |           |           |          |           |          |     |     | Ι,  |

| 0   | 0.0 | ^@       | NUL       | 32       | 20        | SPC       | 64       | 40        | 0        | 96  | 60  |     |

| 1   | 01  | ^A       | SOH       | 33       | 21        | !         | 65       | 41        | A        | 97  | 61  | a   |

| 2   | 02  | ^B       | STX       | 34       | 22        | "         | 66       | 42        | В        | 98  | 62  | b   |

| 3   | 0.3 | ^c       | ETX       | 35       | 23        | #         | 67       | 43        | С        | 99  | 63  | c   |

| 4   | 04  | ^D       | EOT       | 36       | 24        | \$        | 68       | 44        | D        | 100 | 64  | d   |

| 5   | 0.5 | ^E       | ENQ       | 37       | 25        | 8         | 69       | 45        | E        | 101 | 65  | 0   |

| 6   | 0.6 | ^F       | ACK       | 38       | 26        | &         | 70       | 46        | F        | 102 | 66  | f f |

| 7   | 07  | ^G       | BEL       | 39       | 27        |           | 71       | 47        | G        | 103 | 67  | g   |

| 8   | 0.8 | ^H       | BS        | 40       | 28        | (         | 72       | 48        | H        | 104 | 68  | h   |

| 9   | 0.9 | ^I       | HT        | 41       | 29        | )         | 73       | 49        | I        | 105 | 69  | i   |

| 10  | A0  | ^J       | LF        | 42       | 2A        | *         | 74       | 4A        | J        | 106 | 6A  | i   |

| 11  | 0B  | ^K       | VT        | 43       | 2B        | +         | 75       | 4B        | K        | 107 | 6B  | k   |

| 12  | 0C  | ^L       | FF        | 44       | 2C        | ,         | 76       | 4C        | L        | 108 | 6C  | 1   |

| 13  | 0D  | ^M       | CR        | 45       | 2D        | -         | 77       | 4D        | M        | 109 | 6D  | m   |

| 14  | 0E  | ^N       | 30        | 46       | 2E        |           | 78       | 4E        | N        | 110 | 6E  | n   |

| 15  | OF  | ^0       | SI        | 47       | 2F        | /         | 79       | 4 F       | 0        | 111 | 6F  | 0   |

| 16  | 10  | ^P       | DLE       | 48       | 30        | 0         | 80       | 50        | P        | 112 | 70  | p   |

| 17  | 11  | ^0       | DC1       | 49       | 31        | 1         | 81       | 51        | 0        | 113 | 71  | 9   |

| 18  | 12  | ^R       | DC2       | 50       | 32        | 2         | 82       | 52        | R        | 114 | 72  | r   |

| 19  | 13  | ^8       | DC3       | 51       | 33        | 3         | 83       | 53        | 8        | 115 | 73  | 8   |

| 20  | 14  | ^T       | DC4       | 52       | 34        | 4         | 84       | 54        | T        | 116 | 74  | t   |

| 21  | 15  | ^ʊ       | NAK       | 53       | 35        | 5         | 85       | 55        | U        | 117 | 75  | u   |

| 22  | 16  | ^v       | SYN       | 54       | 36        | 6         | 86       | 56        | v        | 118 | 76  | v   |

| 23  | 17  | ^W       | ETB       | 55       | 37        | 7         | 87       | 57        | W        | 119 | 77  | 107 |

| 24  | 18  | ^x       | CAN       | 56       | 38        | 8         | 88       | 58        | x        | 120 | 78  | ×   |

| 25  | 19  | ^¥       | EM        | 57       | 39        | 9         | 89       | 59        | Y        | 121 | 79  | y   |

| 26  | 1A  | ^2       | SUB       | 58       | 3A        | :         | 90       | 5A        | 2        | 122 | 7A  | 2   |

| 27  | 1B  | ^[       | ESC       | 59       | 3B        | ,         | 91       | 5B        | [        | 123 | 7B  | 1   |

| 28  | 1c  | ^\       | FS        | 60       | 3C        | <         | 92       | 5C        | 1        | 124 | 7 C | 1   |

| 29  | 1D  | ^]       | GS        | 61       | 3 D       | =         | 93       | 5D        | 1        | 125 | 7D  | 3   |

| 30  | 1E  | ^^       | RS        | 62       | 3E        | >         | 94       | 5E        | ^        | 126 | 7E  | ~   |

| 31  | 1 F | ^_       | us        | 63       | 3F        | ?         | 95       | 5F        | _        | 127 | 7F  | DI  |

|     |     | Computer | Organisat | ion COMP | 2008 Jami | e Yang: i | /ann@wes | ternsydne | v edu au |     |     |     |

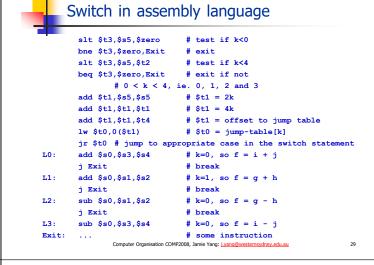

### Switch statement – home EXERCISE

```

switch (k) {

case 0: f = i + j; break; /* k = 0 */

case 1: f = g + h; break; /* k = 1 */

case 2: f = g - h; break; /* k = 2 */

case 3: f = i - j; break; /* k = 3 */

```

- Assume:

- six variables f, g, h, i, j and k correspond to registers \$s0 through to \$s5;

- register \$t2 contains a value 4

- we may code the switch statement as a chain of if-then-else

- another solution: a jump address table

- a table of addresses of a series of instruction sequences (an array of

- Assume \$t4 contains the address of the jump table

- we need an instruction to jump to an address contained in a register

- "jump register" instruction: in MIPS: jr register

Computer Organisation COMP2008, Jamie Yang: j.yang@westernsydney.edu.au

### Recommended readings

| UnitOutline | LearningGuide | Teaching Schedule, | Aligning Assessments & | ascil\_chart.pdf | bias\_representation.pdf | PCSpim.pdf | ascil\_chart.pdf | bias\_representation.pdf | PCSpim.pdf | ascii\_chart.pdf | bias\_representation.pdf | H PCSpim Portable Version | Library materials PH6, §2.2-§2.3, P69: Operations and Operands PH5, §2.2-§2.3, P63: Operations and Operands PH4, §2.2-§2.3, P78: Operations and Operands PH6, §2.2-§2.3, §2.5: 1<sup>st</sup>-3rd Principle of hardware design PH5, §2.2-§2.3, §2.5: 1<sup>st</sup>-3rd Principle of hardware design PH4, §2.2-§2.3, §2.5, P79-P97: 1st-4th Principle of hardware design PH6, §2.5, P86: pay attention to Stored-Program Concept PH5, §2.5, P86: pay attention to Stored-Program Concept PH4, §2.5, P101: pay attention to Stored-Program Concept PH6, §2.7, P96: Understand basic control structures PH5, §2.7, P90-P96: Understand basic control structures PH4, §2.7, P105-P111: Understand basic control structures HP\_AppA.pdf -> A-21: Memory layout

Text readings are listed in Teaching Schedule and Learning Guide

PH6 (PH5 & PH4 also suitable): check whether eBook available on library site

PH6: companion materials (e.g. online sections for further readings)

https://www.elsevier.com/books-andcompanion/9780128201091

PH5: companion materials (e.g. online sections for further readings) 7263/?ISBN=9780124077263

HP\_AppA.pdf-> A-44: System services Computer Organisation COMP2008, Jamie Yang: j.yang@westernsvdnev.edu.au